讲得太好了!电容,去耦和退耦的注意事项

|

01

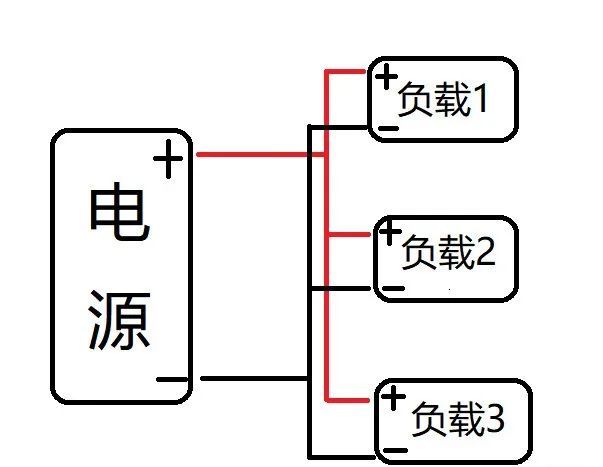

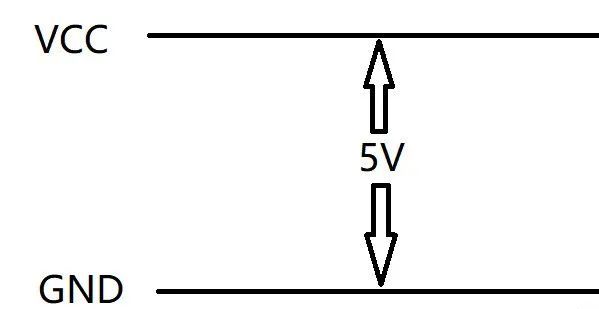

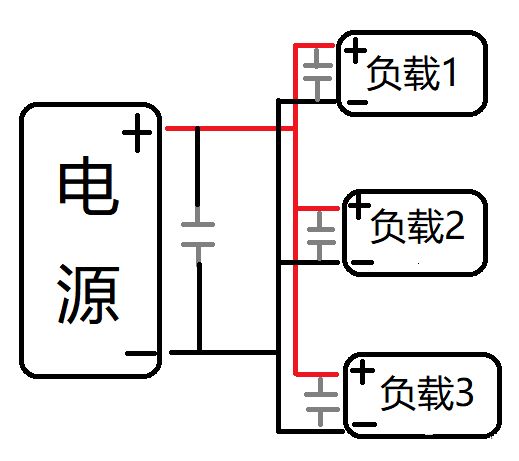

1.简介去耦(decoupling)电容也称退耦电容,一般都安置在元件附近的电源处,用来滤除高频噪声,使电压稳定干净,保证元件的正常工作。 2.分析对于一个电路系统来说,一般有多个负载,这些负载的供电都来自同一个电源。

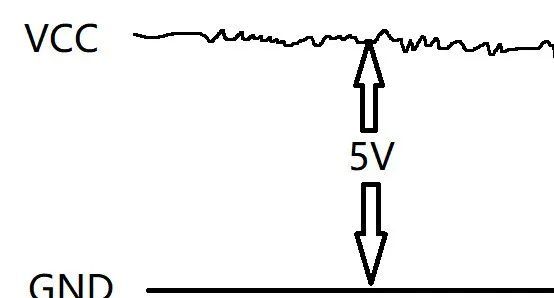

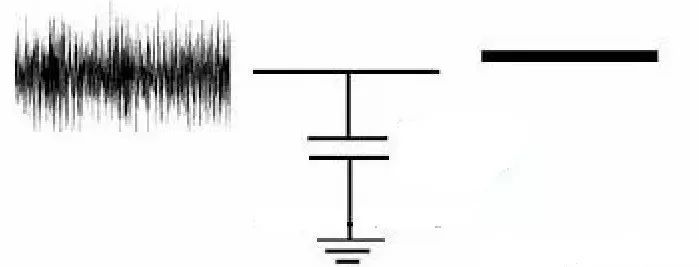

这样耦和了AC的DC供电电压不仅会影响本负载区域内的电路的工作,也会影响到其它连接在同一个VCC上的其它负载的工作,有可能导致那些负载的电路工作出现问题。 解决的方法就是在电源两端并上一个小容量电容从电源上看,没有去耦电容的时候如左侧的波形,加上了去耦电容之后变成了右侧的样子,供电电压的波形变得干净了,我们称该电容的作用是去掉了耦和在干净的DC上的噪声,所以该电容被称之为去耦电容,当然也可以被称之为旁路(Bypass)电容,因为该电容将DC上耦和的噪声给旁路到地上去了,只留下干净的DC给后续的电路供电。

02

1.问题了解了什么是去耦电容后,那么问题来了:究竟需要多大容量的电容才能达到去耦的效果?这么多不同种类的电容选用哪种电容合适呢?为什么在很多电路上看到针对一个电源管脚会有多个容量大小不同、类型也不相同的电容一起工作呢? 2.分析

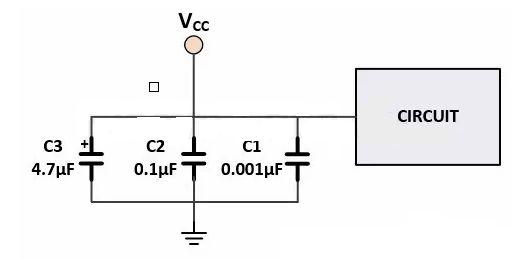

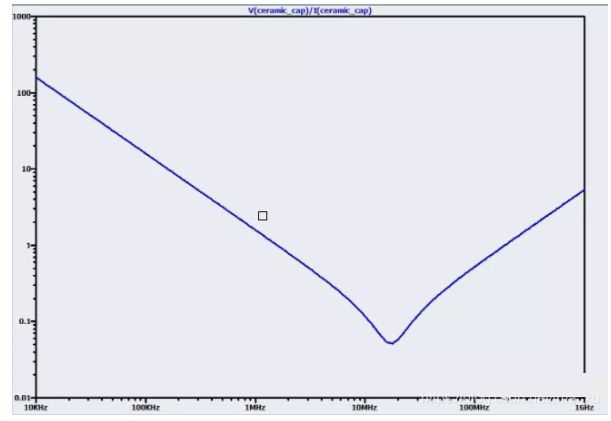

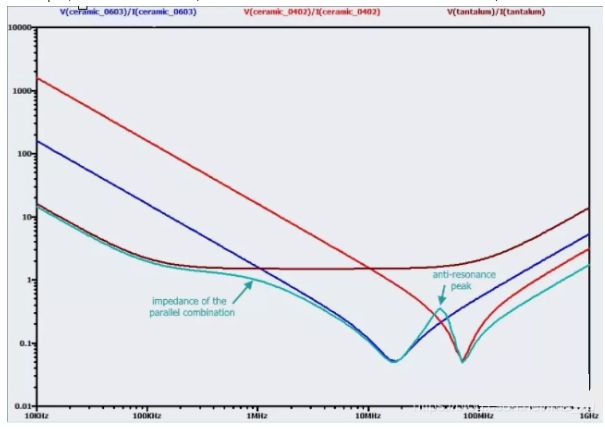

在一个芯片(比如FPGA/MCU)的电源管脚上需要多个不同容值、不同类型的电容并联达到较好的去耦效果。 我们用来去耦的电容器(不论是哪一种)用于在电源线上的瞬态干扰期间快速提供电流,它们都不只有“电容”一个属性,还有两个阻碍电流流动的部分:电阻(ESR) - 无论频率如何都呈现固定阻抗; 电感(ESL)- 随着频率的增加其阻抗也变得更高。而这三部分的值与电容的类型、容值、封装都有很大的关系。 作为最常用的去耦神器 - 陶瓷电容具有很低的ESR和ESL(它们也很便宜),其次是钽电容,提供适中的ESR和ESL,但相对有较高的电容/体积比,因此它们用于更高值的旁路电容,用于补偿电源线上的低频变化。对于陶瓷和钽电容,较大的封装通常意味着较高的ESL。 下图显示了0.1μF,封装为0603的陶瓷电容器的阻抗,该电容器具有850pH的ESL和50mΩ的ESR:

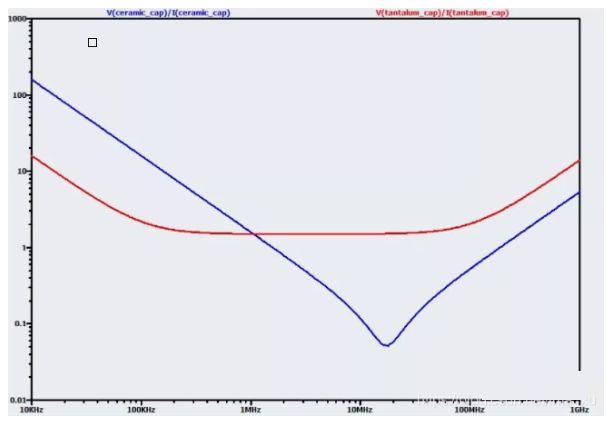

正如前面讨论的,去耦电容的作用就是平滑掉高频变动的纹波电流,理想的电容器可以很容易地实现这一点,因为电容器的阻抗随着频率的增加而降低。但由于ESL的存在,在某个频率下阻抗实际上随频率开始上升,这个频率点又被称为自谐振频率点。我们再对比一下1μF的钽电容器,它有2200pH的ESL和1.5Ω的ESR。

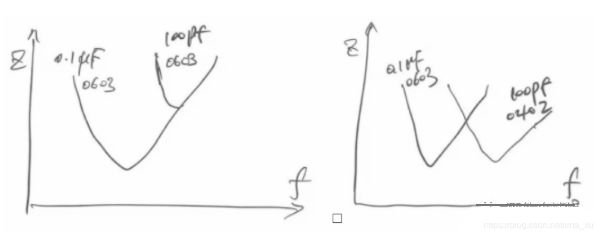

由于其较高的电容值,钽电容器的阻抗在开始阶段低于陶瓷的阻抗,但是较高的ESR和ESL的影响导致阻抗在100kHz附近变平,在1MHz-10MHz高于陶瓷电容的阻抗,在10MHz附近高出陶瓷的阻抗10倍。设想一下,如果电路中的噪声频率是在10MHz左右,即使钽电容具有更高的电容,也不如放置一颗0.1μF的陶瓷电容更有效。如果我们要旁路掉更高频率的噪声,即使这个陶瓷电容也会存在太大的阻抗,我们就需要更低的ESL,也就是更小的封装。下图左侧表明两个同样是0603封装的电容并不改变其对高频噪声的去偶性能,只是相当于去耦电容的容量为二者的和而已,后面看到这个容量对旁路噪声的效果其实没有什么差别;而下图的右侧,一个0.1μF封装为0603的电容和100pF封装为0402的电容并联在一起,就可以覆盖更宽的高频范围,能够对两个频点的噪声进行去偶。

回到本篇文章第一个图,在同一个电源管脚并联了三个去耦电容: 4.7μF的钽电容,对比较低频率的噪声滤除比较有效;0.1μF、0603的陶瓷电容,对1-50MHz区域的噪声滤除效果比钽电容有效;0.001μF、0402的陶瓷电容,对于50MHz以上的高频噪声滤除比较有效;

所以,不同类型,不同容量,不同封装的电容,去耦的有效频率段也是不同的

03

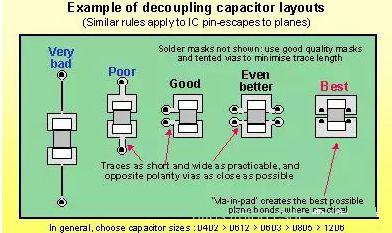

1.原理先看一个很形象的动图,直观体会一下一个电容放置位置不同起到的作用有多大的差异。

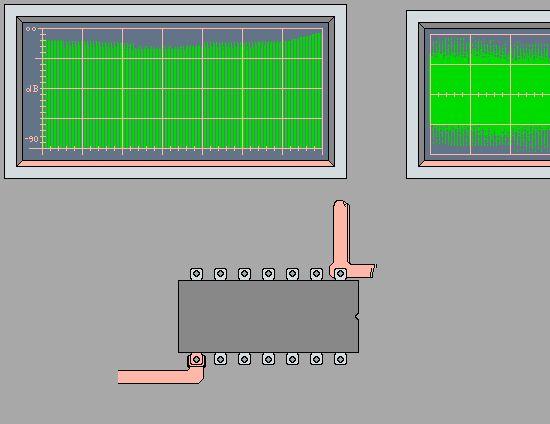

这张动图传递了如下的信息: 在电源管脚上放置一个104(0.1μF)的电容能够有效抑制电源上的噪声,也就是能够对电源噪声去耦;“电源 – 去耦电容 – 地”三点一线的距离越近,则去耦的效果越好;相同材料的电容,即便电容容量减少为1/10,去耦的效果并不会有什么明显变化,我们对于高频去耦用同样封装的器件,容值为0.01μF、0.1μF、1μF效果相差不大;同样容值,贴片(SMD)封装的电容比穿孔的电容效果更好,原因就是穿孔电容的管脚等效的电感要大很多,影响了去耦的效果;电源平面和地平面的使用,一方面可以让三点一线的路径更短,而且两个平面相当于一个大电容,也起到了去耦的作用 2. 实例来看具体的实例。

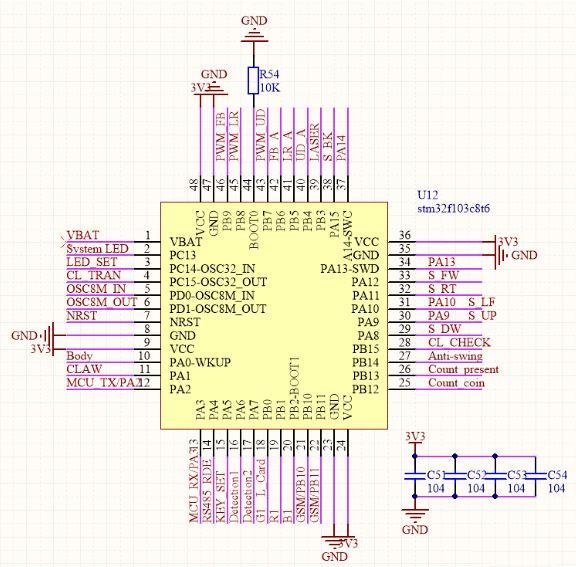

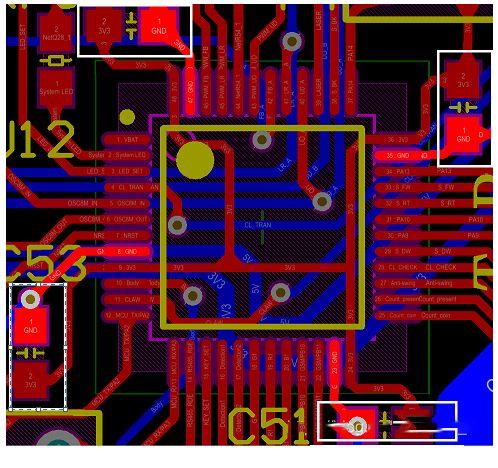

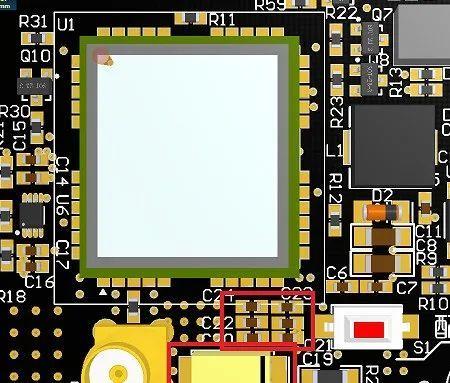

在常用单片机stm32f103c8t6最小系统中,常常有这样四个去耦电容,分别对应芯片的四对供电引脚。而在PCB中,这四个电容(图中白色框框中)在摆放合理的情况下越靠近mcu越好。

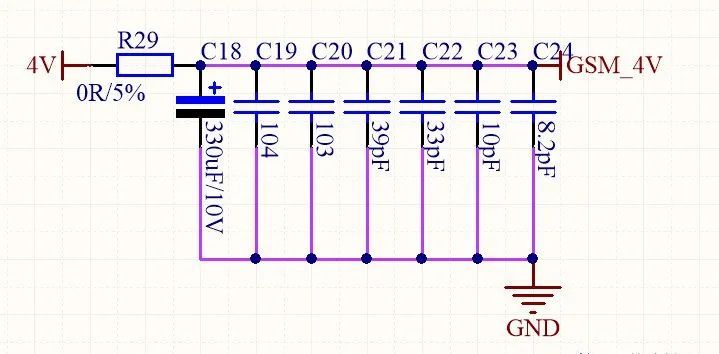

而在多电容去耦(对电源稳定要求极为苛刻的电路中),比如GSM的电源,需要多个不同容量/种类的电容。

04

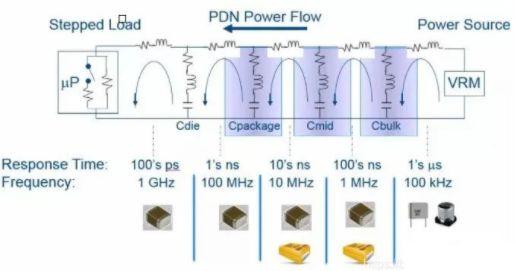

下图是一个实际电子产品系统的供电分布网络,为了强调噪声的起源(最左侧),把电源模块(VRM)放到了最右侧。PCB上的走线、过孔、相关的器件引脚等都会产生寄生电阻、电感等,在图中以R L的方式等效表达出来。在这个图中可以看出针对IC器件内部(Die)、针对整个IC器件(Package)、针对某一个功能模块中的电路单元都有相应的去耦电容,最左侧(靠近内核)采用频率响应很高的小容值、小封装的陶瓷电容,到右侧则是低频率、容量比较大的电解电容。

总之一句话:去耦电容的PCB布局摆放原则是最小化电阻,最小化电感。 |