桥T线圈电路的实现与设计

|

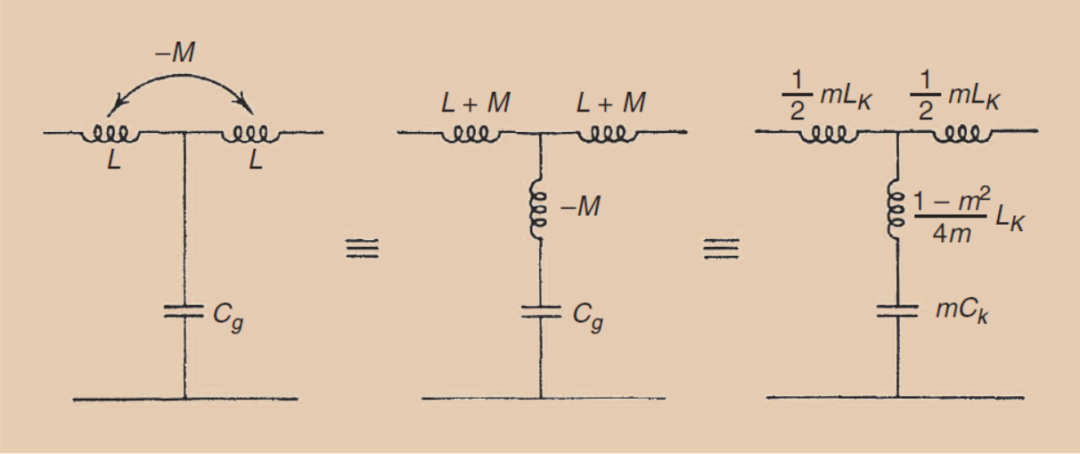

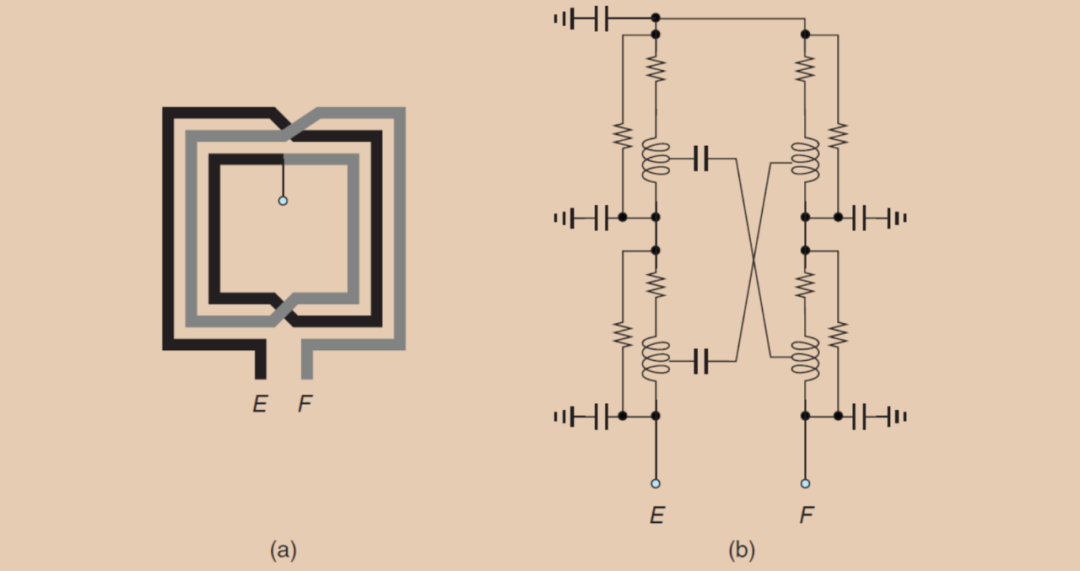

T线圈在集成电路设计中有着非常重要的地位,尤其是高速电路设计的I/O单元、宽带匹配等电路中有广泛应用。本文翻译拉扎维发表在《A Circuit for All Seasons》杂志上关于T线圈的文章,非常具有参考价值。 The Bridged T-Coil 桥T线圈 By Behzad Razavi(拉扎维) 桥T线圈(The bridged T-coil),通常称为T线圈(T-coil),是一种电路拓扑结构,其带宽扩展性能要大于电感峰化(inductive peaking)。如今的许多高速放大器(high-speed amplifier)、线路驱动器(line driver)以及输入/输出接口(input/output interfaces, I/O)在应对寄生电容时都会在芯片上整合T线圈。在这篇文章中,我们将介绍和分析其基本结构,并研究其应用。 简短历史 线圈电路可以追溯到1948年Ginzton等人对分布式放大器的经典论文。作者们将这个结构称为"桥T连接",并将其与等效电路一起呈现,如图1所示。

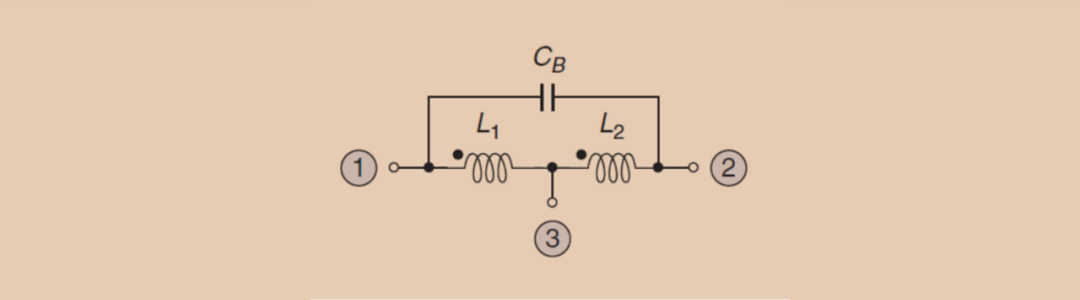

图1:1948年由Ginzton等人描述的桥T线圈电路。 T线圈在带宽增强方面的应用始于1960年代末的Tektronix工程师。他们需要为示波器(oscilloscope)的前端(front end)设计快速的"垂直"放大器,这促使他们创新了许多宽带电路技术,并且Tektronix的设计师们看到了T线圈的显著优势。仪器制造商对T线圈电路的设计细节保密了很多年。直到1990年,前Tektronix工程师Dennis Feucht在他的书中公开了T线圈的设计方程。 早期的T线圈实现主要基于分立的、非片上的电感或变压器,但会受到电路板寄生效应、键合线电感,以及与其他信号之间的不期望的耦合的影响。1980年代末和1990年代初出现了一些GaAs工艺集成电路的实现。随着1990年代射频电路的革命和对集成电感的巨大工作,T线圈必然也会找到其在CMOS芯片上的位置。当然,芯片结构的有限Q值和寄生电容会带来新的问题。此外,还需要在两个螺旋电感之间创建一个明确的耦合因子。2003年,有两篇论文描述了集成T线圈的设计以及它们在宽带驱动器(broadband driver)和静电放电保护电路(ESD protection)中的应用。 基本思想 桥T线圈是双端桥T网络的一种特例。它由两个相互耦合的电感和一个桥接电容组成(如图2)。耦合极性很重要,而这两个电感值通常选择是相等的。当某些负载连接到这个电路时,节点1或2处看到的阻抗以及从这些节点到节点3的传输函数会呈现出一些有趣的特性。

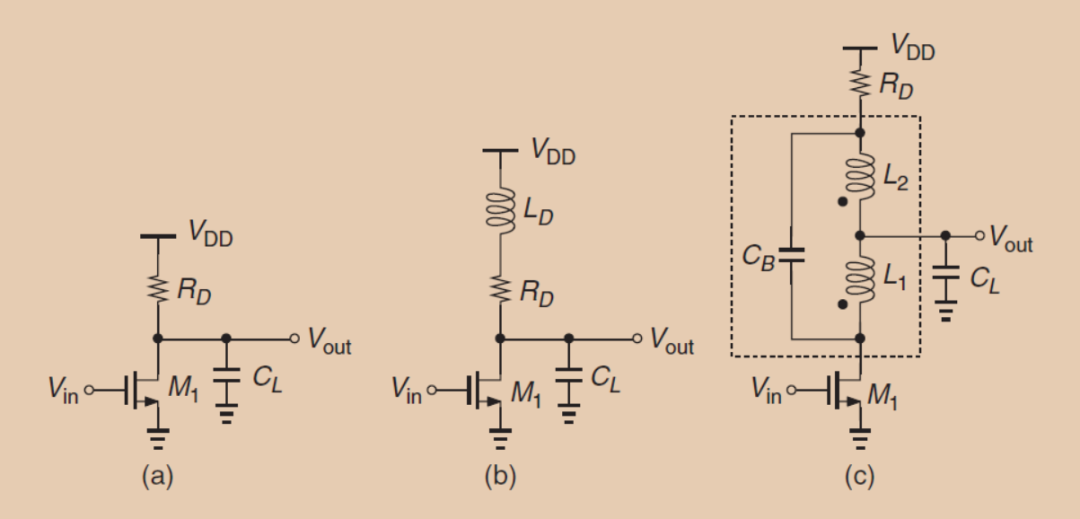

图2:基本的桥T线圈结构 例如,考虑图3(a)中显示的简单共源级,其具有负载电容的电路。在高频时,的小信号漏电流会被分流,导致下降。我们可以将一个电感并联在上[图3(b)],使和的串联阻抗随频率增加,从而强迫更多的电流通过,从而减少总增益的下降。或者,我们可以在信号路径中插入一个T线圈电路,如图3(c)所示。我们关心的是传输函数及其作为组件值函数的行为。

图3:共源级与(a)简单的电阻负载,(b)电感峰化(inductive peaking)和(c)T线圈峰化(T-coil peaking) 传输函数可以使用额外元定理(Extra Element Theorem,EET)或变换得出,具体如下: 其中, 这里,表示图3(c)中显示的和之间的互感。这个传输函数没有提供太多的直观感受,但是其中的一个特例在数学和实际应用上都更易处理。我们假设,并选择这样的值,使得公式(1)中的零点被两个极点抵消。如文献中所示,如果满足以下两个条件,这就可以实现, 其中是耦合系数,等于,并且 得到的二阶传输函数形式如下 其中 对于设计目的,我们选择阻尼因子的值,并希望确定其他电路参数。解上述方程,由文献得出, 这些结果与文献中的结果一致。值得注意的是,随增加,即更紧密的耦合对应更有阻尼的响应。

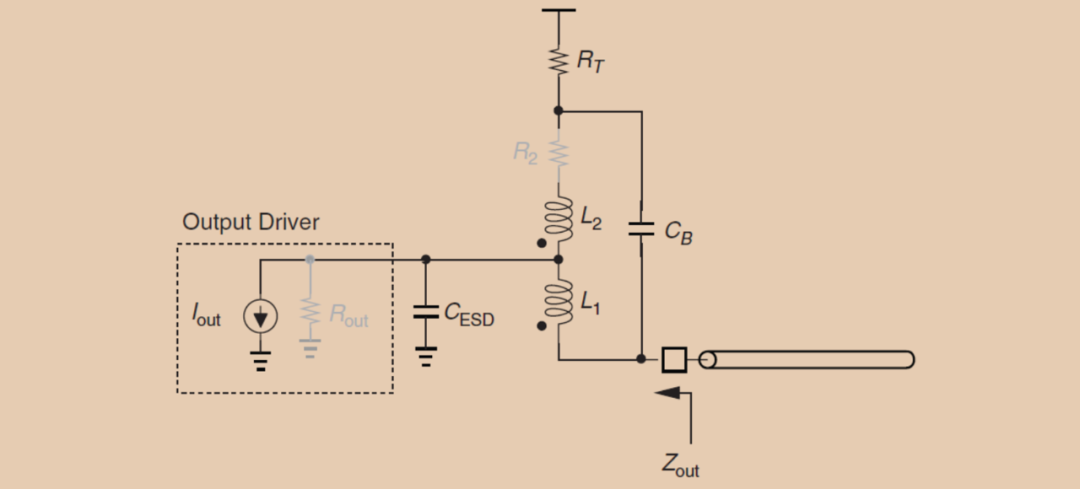

FICURE 4: (a) An input network with an ESD device and (b) an input network using a T-coil for broadband matching.图4:(a)带有ESD器件的输入网络和(b)使用T线圈进行宽带匹配的输入网络。 带宽优势 如上所述,桥T线圈比电感峰化更大程度地提高了速度。我们通过考虑两种情况下的3dB带宽来阐述这种优势。从(10)中,T线圈的带宽表达为: 我们用公式(14)替换,用公式(13)替换,得到: 例如,如果,那么。值得注意的是,T线圈将原始带宽乘以了2.83的因子。相比之下,图3(b)的电感峰化阶段对于的带宽大约是。(更准确的比较应该同时考虑到时域过冲。) ESD保护 除了扩大带宽,T线圈在存在重负载电容的情况下也可以创建一个固定、阻性的输入阻抗,这是在ESD保护电路中常见的情况。例如,在图4(a)所示的输入网络中,其中是终端电阻,ESD器件电容会恶化输入匹配特性,从而导致反射。另一方面,如果按如图4(b)所示插入一个桥T线圈,可以在所有频率下都等于 。我们可以在两个极端直观地感受到这个特性:在非常低的频率下,和将短接到输入端,在高频时,做同样的事情。可以证明,如果,并且满足公式(10)的极-零抵消的条件也成立,则在所有频率下。换句话说,公式(13)-(15)所规定的条件在这里也同样适用。 直观的说明也可以解释为什么在这种情况下T线圈不能有零点。如果电路确实包含一个零点,那么在零点频率处,必须仍然需要等于终端阻抗。现在假设我们用的形式驱动图3(c)的电路,得到。因此,可以去掉。换句话说,对于,漏端电荷减少到了并联和的组合。这种组合在时不能有零阻抗,因此。 使用ESD保护的输出驱动器也可以类似地从T线圈中受益。如图5所示,这种设计假设驱动级的输出阻抗为无穷大,并向外界呈现等于的阻抗。如果输出阻抗,不够高,可以将一个小阻抗串联在上来补偿其效果。这个阻抗由给出。 T线圈的实现 在这种特殊情况下,电感可以采用对称螺旋的形式简单地实现[图6(a)] 。在这里,线间距被选择来调整所需的互感,外部尺寸和圈数提供所需的电感。为了在仿真中包含螺旋线的寄生电阻和电容,可以构造一个分布的模型,如图6(b)所示。注意,也考虑到了线圈间电容。作为一阶(jìn)似,这个电容出现在和之间,并可以从桥电容中减去。

图5:使用T线圈的输出驱动

图6:(a)T线圈的实现和(b)用于电路仿真的分布模型 与其他技术的结合 桥T线圈网络可以与其他高速拓扑结合,以实现更大的带宽。例如,由于二阶T线圈电路的输入阻抗是恒定的,人们可以在输入信号路径中直接添加串联峰化。如图7所示,这种组合在两种情况下都很有用:1)如果一级包含一个大的晶体管[图7(a)],会遭受高输出电容;2)如果一个输入网络必须容纳一个大的ESD电容[图7(b)],在这种情况下,两个电容器都可以代表ESD器件。串联峰化也可以应用到如图5所示的输出网络。

图7:在(a)具有高输出电容的增益级和(b)具有高ESD电容的输入网络中,串联峰化和T线圈的使用。 差分电路可以将T线圈与其他差分技术结合。例如,如图8所示,可以添加一个使用交叉耦合对的负电容发生器并联于负载电容,从而提高整体速度。为了避免在时间响应中产生大的过冲,我们选择。

图8:在T线圈中增加负电容发生器。 给读者的问题 使用功率损耗论证来确定图4(b)中电路的传输函数。 在图7(a)中,如果串联峰化网络的阻尼因子必须保持在附(jìn),那么应该如何选择? 审核编辑:汤梓红 |