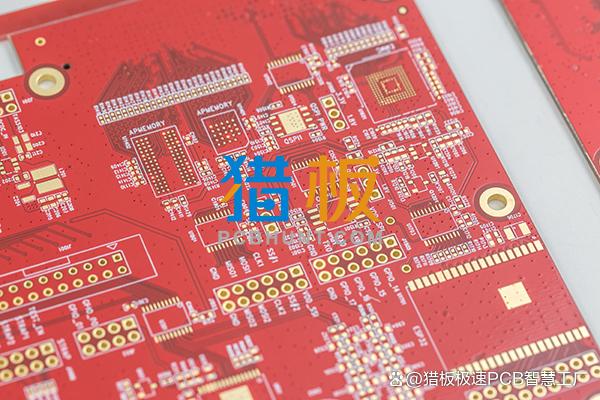

薄PCB打样过程中PCB串扰如何体现?

|

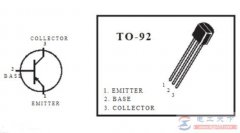

串扰是一个信号受到另一个信号的无意影响或对另一个信号的无意影响。电场和磁场的复杂相互作用导致在没有物理接触(但也许是“物理”?)的情况下影响导体线路的能力。相声可以在两种不同的模式下发生。这些模式包括接触式和非接触式。减少串音的影响需要首先诊断其原因: 直接:也被称为“导电串扰”,两个接触的导体可以通过它们之间的整个频率范围,包括直流偏置(也称为零频率响应)。然后,任何直流信号都不加抑制地通过,由此产生的信号在电路输入或输出处经历一些偏移误差。 间接:信号也仅通过电场或磁场耦合,导致电容或电感耦合。电容耦合,或者称为交流耦合,从信号中消除直流偏置,以防止与电压不匹配相关的问题。同时,电感耦合是变压器和其他各种机电设备的核心。然而,当它无意中出现时,它可能会对性能产生负面影响。

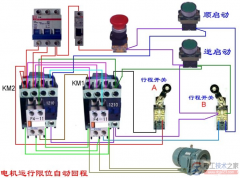

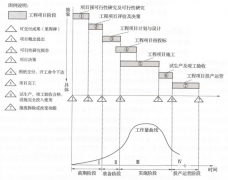

DFM进程防止耦合 任何导体相交的地方,都不需要在设计或制造层面采取纠正措施。例如,不良的焊料应用/去除和后期生产过程,如导致枝晶生长和自发晶须的电迁移,可能会造成短路。由于这些缺陷是次要过程,设计只能预测产生导电串扰的条件,并试图通过电池老化和环境测试来最小化其影响,以指导未来的修订(如有必要)。 由于制造过程中的错误或粗心,由于规则检查,导电耦合不太可能发生,但电容和电感耦合可能更严重。由于场强随距离迅速减小,解决间接耦合的最佳方法是将迹线分开移动,无论是在平面内还是在不同的平面上。一个特别强的信号可以通过在信号层上淹没地面来进一步隔离,以改善信号与地面的耦合。 一般相声注意事项和解决方案 距离走线是一种很好的做法,但由于空间限制,在HDI设计中很难实现。相反,设计师可以通过列出一些布局中常见的麻烦部分来对抗串扰: 混合信号设计:混合信号设计的一个基石是将模拟信号与数字信号隔离开来,并对地平面进行划分,以防止高频数字信号带来的背景噪声。然而,设计师可以更进一步。将模拟信号大致按频率分组,以防止攻击线耦合到较低频率的受害线。CMOS元件的价值在于功率效率,并且具有高边缘速率,这也会影响周围的信号。在CMOS部件周围提供足够的间距,特别是模拟信号。 时序问题:时钟线,即使是数字的,也是噪声易感性的候选者。当信号的真实周期性出现偏差(也称为抖动)时,可以检测到这一点。确保驱动程序使用统一的时钟频率。单个封装中的多个时钟将显著降低信噪比(SNR)。 嵌入式信号层:对于四层压合,最常见的安排是信号走线在顶部和底部,接地在两个,电源在三个。然而,高频设计可能需要利用反转:信号在内层与平面在外层额外屏蔽。这一步骤减少了相声的总体机会和强度(如果采用了良好的布局实践),但也存在一些缺点。由于信号走线的可访问性和可见性,电路板的原型设计变得更具挑战性,而解耦受到限制,故障排除的难度也增加了。 |